### Foreword

• This chapter describes Huawei's Ascend AI chips, and hardware and software architectures of Ascend chips, and full-stack all-scenario solutions of Ascend AI chips.

# Objectives

On completion of the course, you will be able to:

- Get an overview of Al chips.

- Understand hardware and software architectures of Huawei Ascend chips.

- Learn about Huawei Atlas AI computing platform.

- Understand industry applications of Atlas.

#### 1. Overview of AI Chips

- **■** Summary

- Classification of Al Chips

- Current Status of Al Chips

- GPU, TPU, and Ascend 310 Design Comparison

- Ascend Al Processors

- 2. Hardware Architecture of Ascend Chips

- 3. ...

## Overview and Objectives

This section is an overview of AI chips, including the introduction, classification, and status of AI chips, comparison between GPUs and CPUs, and introduction of Ascend AI processors.

### **Definition**

- Four elements of AI: data, algorithm, scenario, and computing power

- Al chips, also known as Al accelerators, are function modules that process massive computing tasks in Al applications.

#### 1. Overview of AI Chips

- Summary

- Classification of AI Chips

- Current Status of Al Chips

- Design Comparison of GPUs and CPUs

- Ascend Al Processors

- 2. Hardware Architecture of Ascend Chips

- 3. ...

### Classification of AI Chips (1)

- Al Chips can be divided into four types by technical architecture:

- A central processing unit (CPU): a super-large-scale integrated circuit, which is the computing core and

control unit of a computer. It can interpret computer instructions and process computer software data.

- A graphics processing unit (GPU): a display core, visual processor, and display chip. It is a microprocessor that processes images on personal computers, workstations, game consoles, and mobile devices, such as tablet computers and smart phones.

- An application specific integrated circuit (ASIC): an integrated circuit designed for a specific purpose.

- A field programmable gate array (FPGA): designed to implement functions of a semi-customized chip. The

hardware structure can be flexibly configured and changed in real time based on requirements.

### Classification of AI Chips (2)

- Al chips can be divided into training and inference by business application.

- In the training phase, a complex deep neural network model needs to be trained through a large number of data inputs or an unsupervised learning method such as enhanced learning. The training process requires massive training data and a complex deep neural network structure. The huge computing amount requires ultra-high performance including computing power, precision, and scalability of processors. Nvidia GPU cluster and Google TPUs are commonly used in AI training.

- Inferences are made using trained models and new data. For example, a video surveillance device uses the background deep neural network model to recognize a captured face. Although the calculation amount of the inference is much less than that of training, a large number of matrix operations are involved. GPU, FPGA and ASIC are also used in the inference process.

#### 1. Overview of AI Chips

- Summary

- Classification of Al Chips

- Current Status of Al Chips

- Design Comparison of GPUs and CPUs

- Ascend Al Processors

- 2. Hardware Architecture of Ascend Chips

- 3. ...

### Current Status of Al Chips - CPU

- Central processing unit (CPU)

- The computer performance has been steadily improved based on the Moore's Law.

- The CPU cores added for performance enhancement also increase power consumption and cost.

- Extra instructions have been introduced and the architecture has been modified to improve AI performance.

- Instructions, such as AVX512, have been introduced into Intel processors (CISC architecture) and vector computing modules, such as

FMA, into the ALU computing module.

- Instruction sets including Cortex A have been introduced into ARM (RISC architecture), which will be upgraded continuously.

- Despite that boosting the processor frequency can elevate the performance, the high frequency will cause huge power consumption and overheating of the chip as the frequency reaches the ceiling.

### Current Status of Al Chips - GPU

- Graph processing unit (GPU)

- GPU performs remarkably in matrix computing and parallel computing and plays a key role in heterogeneous computing. It was first introduced to the AI field as an acceleration chip for deep learning.

Currently, the GPU ecosystem has matured.

- Using the GPU architecture, NVIDIA focuses on the following two aspects of deep learning:

- Diversifying the ecosystem: It has launched the cuDNN optimization library for neural networks to improve usability and optimize the GPU underlying architecture.

- Improving customization: It supports various data types, including int8 in addition to float32; introduces modules dedicated for deep learning. For example, the optimized architecture of Tensor cores has been introduced, such as the TensorCore of V100.

- The existing problems include high costs and latency and low energy efficiency.

### **Current Status of AI Chips - TPU**

- Tensor processing unit (TPU)

- Since 2006, Google has sought to apply the design concept of ASICs to the neural network field and released TPU, a customized AI chip that supports TensorFlow, which is an open-source deep learning framework.

- Massive systolic arrays and large-capacity on-chip storage are adopted to accelerate the most common convolution operations in deep neural networks.

Systolic arrays optimize matrix multiplication and convolution operations to elevate computing power and lower

energy consumption.

### Current Status of Al Chips - FPGA

- Field programmable gate array (FPGA)

- Using the HDL programmable mode, FPGAs are highly flexible, reconfigurable and re-programmable, and customizable.

- Multiple FPGAs can be used to load the DNN model on the chips to lower computing latency. FPGAs outperform GPUs in terms of computing performance. However, the optimal performance cannot be achieved due to continuous erasing and programming. Besides, redundant transistors and cables, logic circuits with the same functions occupy a larger chip area.

- The reconfigurable structure lowers supply and R&D risks. The cost is relatively flexible depending on the purchase quantity.

- The design and tapeout processes are decoupled. The development period is long, generally half a year.

The entry barrier is high.

#### 1. Overview of AI Chips

- Summary

- Classification of AI Chips

- Current Status of AI Chips

- Design Comparison of GPUs and CPUs

- Ascend Al Processors

- 2. Hardware Architecture of Ascend Chips

- 3. Software Architecture of Ascend Chips

- 4. ..

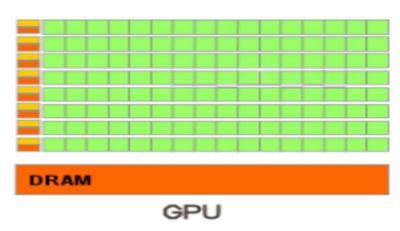

### Design Comparison of GPUs and CPUs

- GPUs are designed for massive data of the same type independent from each other and pure computing environments that do not need to be interrupted.

- Each GPU comprises several large-sized parallel computing architectures with thousands of smaller cores designed to handle multiple tasks simultaneously.

- Throughput-oriented design

- With many ALUs and few caches, which improve services for threads, unlike those in CPU. The cache merges access to DRAM, causing latency.

- The control unit performs combined access.

- A large number of ALUs process numerous threads concurrently to cover up the latency.

- Specialized in computing-intensive and easy-to-parallel programs

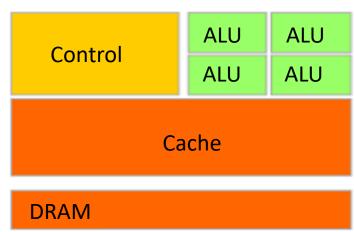

### Design Comparison of GPUs and CPUs

- CPUs need to process different data types in a universal manner, perform logic judgment, and introduce massive branch jumps and interrupted processing.

- Composed of several cores optimized for sequential serial processing

- Low-latency design

- The powerful ALU unit can complete the calculation in a short clock cycle.

- The large cache lowers latency.

- High clock frequency

- Complex logic control unit, multi-branch programs can reduce latency through branch prediction.

- For instructions that depend on the previous instruction result, the logic unit determines the location of the instructions in the pipeline to speed up data forwarding.

- Specialized in logic control and serial operation

#### 1. Overview of AI Chips

- Summary

- Classification of AI Chips

- Current Status of AI Chips

- Design Comparison of GPUs and CPUs

- Ascend Al Processors

- 2. Hardware Architecture of Ascend Chips

- 3. Software Architecture of Ascend Chips

- 4. ..

#### Ascend Al Processors

- Neural-network processing unit (NPU): uses a deep learning instruction set to process a large number of human neurons and synapses simulated at the circuit layer. One instruction is used to process a group of neurons.

- Typical NPUs: Huawei Ascend Al chips, Cambricon chips, and IBM TrueNorth

- Ascend-Mini

- Architecture: Da Vinci

- Half precision (FP16): 8 Tera-FLOPS

- Integer precision (INT8): 16 Tera-OPS

- 16-channel full-HD video decoder: H.264/H.265

- 1-channel full-HD video decoder: H.264/H.265

- Max. power: 8W

- 12nm FFC

- Ascend-Max

- Architecture: Da Vinci

- Half precision (FP16): 256 Tera-FLOPS

- Integer precision (INT8): 512 Tera-OPS

- 128-channel full-HD video decoder: H.264/H.265

- Max. power: 350W

- 7nm

# **Section Summary**

• This section describes AI chips, including classification of AI chips by technologies and functions, AI chip ecosystem, and comparison between GPUs and CPUs.

- 1. Overview of Al Chips

- 2. Hardware Architecture of Ascend Chips

- Logic Architecture of Ascend Al Processors

- Da Vinci Architecture

- 3. Software Architecture of Ascend Chips

- 4. Huawei Atlas Al Computing Platform

- 5. Industry Applications of Atlas

## Overview and Objectives

• This section describes the hardware architecture of Ascend chips, including the logic architecture of the Ascend AI processors and Da Vinci architecture.

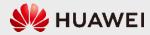

### Logic Architecture of Ascend Al Processors

- Ascend Al processor consist of:

- Control CPU (synchronization)

- Al computing engine, including Al core and Al CPU (昇腾Al芯片的计算核心,主要负责执行矩阵、向量、 标量计算密集的算子任务)

- Multi-layer system-on-chip (SoC) caches or buffers (temp storage)(专用于AI Core、AI CPU,提供高带宽、 低延迟的memory访问)

- □ Digital vision pre-processing (DVPP) module (数字视觉预处理等系统。完成图像视频的编解码)

Interface

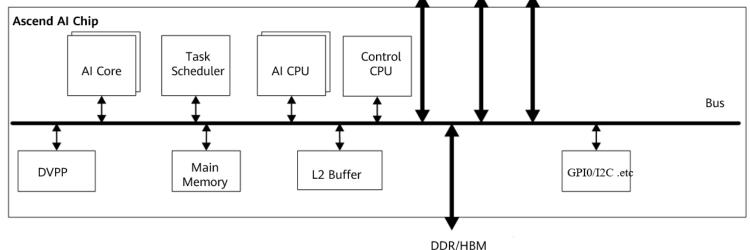

### **DVPP**

DVPP(Digital Video Pre-Processor): image/video encoding, decoding, resizing, cropping, format conversion.

- 1. Overview of Al Chips

- 2. Hardware Architecture of Ascend Chips

- Logic Architecture of Ascend Al Processors

- Da Vinci Architecture

- 3. Software Architecture of Ascend Chips

- 4. Huawei Atlas Al Computing Platform

- 5. Industry Applications of Atlas

### Ascend Al Computing Engine - Da Vinci Architecture

One of the four major architectures of Ascend AI processors is the AI computing engine, which consists of the AI core (Da Vinci architecture) and AI CPU. The Da Vinci architecture developed to improve the AI computing power serves as the core of the Ascend AI computing engine and AI processor.

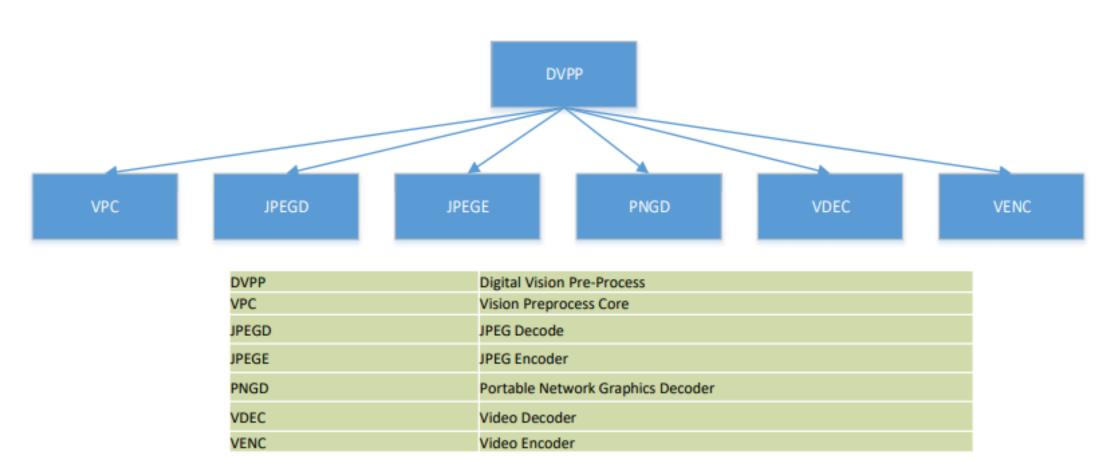

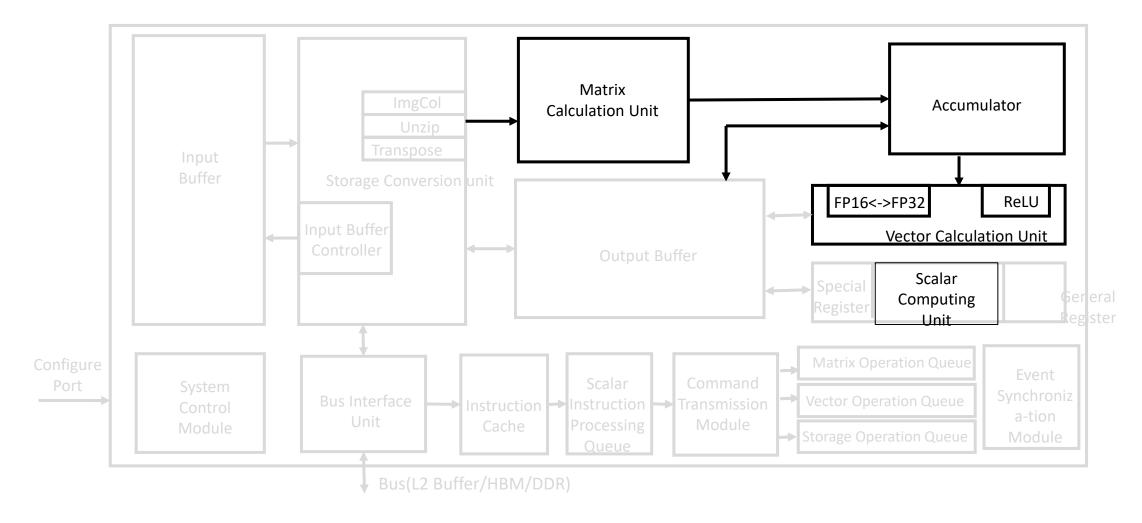

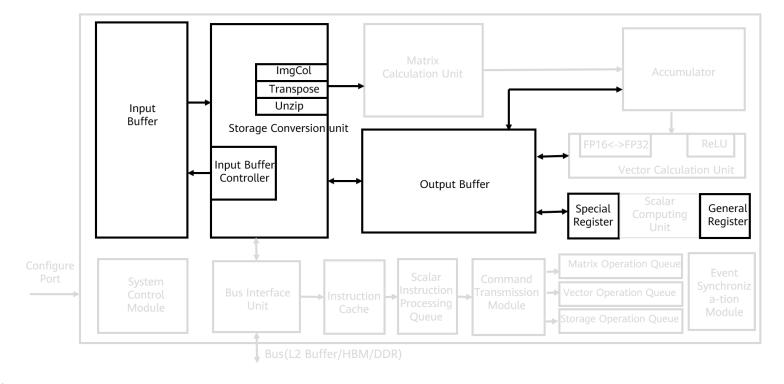

### Da Vinci Architecture (Al Core)

- Main components of the Da Vinci architecture:

- Computing unit: It consists of the cube unit, vector unit, and scalar unit.

- Storage system: It consists of the on-chip storage unit of the AI core and data channels.

- Control unit provides instruction control for the entire computing process. It is equivalent to the command center of the AI core and is responsible for the running of the entire AI core.

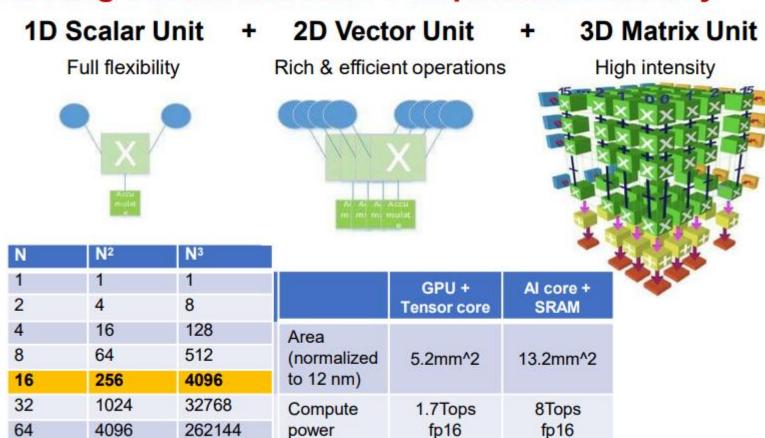

### Da Vinci Architecture (Al Core) - Computing Unit

- Three types of basic computing units: cube, vector, and scalar units, which correspond to matrix, vector and scalar computing modes respectively.

- Cube computing unit: The matrix computing unit and accumulator are used to perform matrix-related operations. Completes a matrix (4096) of 16x16 multiplied by 16x16 for FP16, or a matrix (8192) of 16x32 multiplied by 32x16 for the INT8 input in a shot.

- Vector computing unit: Implements computing between vectors and scalars or between vectors. This function covers various basic computing types and many customized computing types, including computing of data types such as FP16, FP32, INT32, and INT8.

- Scalar computing unit: Equivalent to a micro CPU, the scalar unit controls the running of the entire AI core. It implements loop control and branch judgment for the entire program, and provides the computing of data addresses and related parameters for cubes or vectors as well as basic arithmetic operations.

### **Building Blocks and their Computation Intensity**

## Da Vinci Architecture (Al Core) - Computing Unit

### Da Vinci Architecture (Al Core) - Storage System (1)

- The storage system of the AI core is composed of the storage unit and corresponding data channel.

- The storage unit consists of the storage control unit, buffer, and registers:

- Storage control unit: The cache at a lower level than the AI core can be directly accessed through the bus interface. The memory can also be directly accessed through the DDR or HBM. A storage conversion unit is set as a transmission controller of the internal data channel of the AI core to implement read/write management of internal data of the AI core between different buffers. It also completes a series of format conversion operations, such as zero padding, Img2Col, transposing, and decompression.

- Input buffer: The buffer temporarily stores the data that needs to be frequently used so the data does not need to be read from the AI core through the bus interface each time. This mode reduces the frequency of data access on the bus and the risk of bus congestion, thereby reducing power consumption and improving performance.

- Output buffer: The buffer stores the intermediate results of computing at each layer in the neural network, so that the data can be easily

obtained for next-layer computing. Reading data through the bus involves low bandwidth and long latency, whereas using the output buffer

greatly improves the computing efficiency.

- Register: Various registers in the AI core are mainly used by the scalar unit.

## Da Vinci Architecture (Al Core) - Storage System (2)

- Data channel: path for data flowing in the AI core during execution of computing tasks

- A data channel of the Da Vinci architecture is characterized by multiple-input single-output. Considering various types and a large quantity of input data in the computing process on the neural network, parallel inputs can improve data inflow efficiency. On the contrary, only an output feature matrix is generated after multiple types of input data are processed. The data channel with a single output of data reduces the use of chip hardware resources.

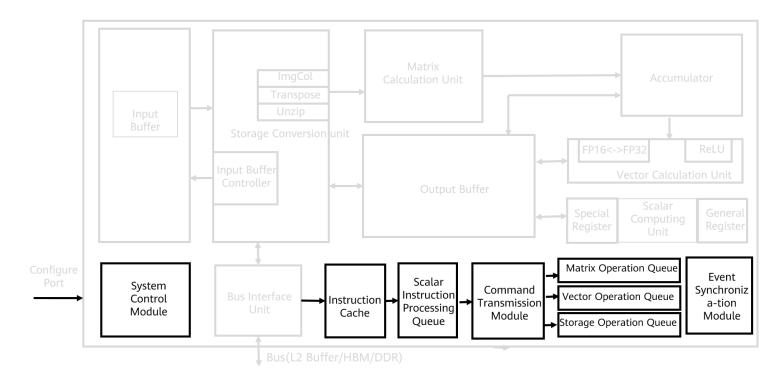

### Da Vinci Architecture (Al Core) - Control Unit (1)

- The control unit consists of the system control module, instruction cache, scalar instruction processing queue, instruction transmitting module, matrix operation queue, vector operation queue, storage conversion queue, and **event synchronization** module.

- System control module: Controls the execution process of a task block (minimum task computing granularity for the AI core). After the task block is executed, the system control module processes the interruption and reports the status. If an error occurs during the execution, the error status is reported to the task scheduler.

- Instruction cache: Prefetches subsequent instructions in advance during instruction execution and reads multiple instructions into the cache at a time, improving instruction execution efficiency.

- Scalar instruction procession queue: After being decoded, the instructions are imported into a scalar queue to implement address

decoding and operation control. The instructions include matrix computing instructions, vector calculation instructions, and storage

conversion instructions.

- Instruction transmitting module: Reads the configured instruction addresses and decoded parameters in the scalar instruction queue, and sends them to the corresponding instruction execution queue according to the instruction type. The scalar instructions reside in the scalar instruction processing queue for subsequent execution.

## Da Vinci Architecture (Al Core) - Control Unit (2)

- Instruction execution queue: Includes a matrix operation queue, vector operation queue, and storage conversion queue. Different instructions enter corresponding operation queues, and instructions in the queues are executed according to the entry sequence.

- Event synchronization module: Controls the execution status of each instruction pipeline in real time, and analyzes dependence relationships between different pipelines to resolve problems of data dependence and synchronization between instruction pipelines.

# **Section Summary**

• This section describes the hardware architecture of Ascend chips, including the computing unit, storage unit, and control unit of the core Da Vinci architecture.

- 1. Overview of Al Chips

- 2. Hardware Architecture of Ascend Chips

- 3. Software Architecture of Ascend Chips

- Logic Architecture of Ascend 310

- Neural Network Software Flow of Ascend 310

- Data Flowchart of Ascend 310

- 4. Huawei Atlas Al Computing Platform

- 5. Industry Applications of Atlas

## Overview and Objectives

• This section describes the software architecture of Ascend chips, including the logic architecture and neural network software flow of Ascend AI processors.

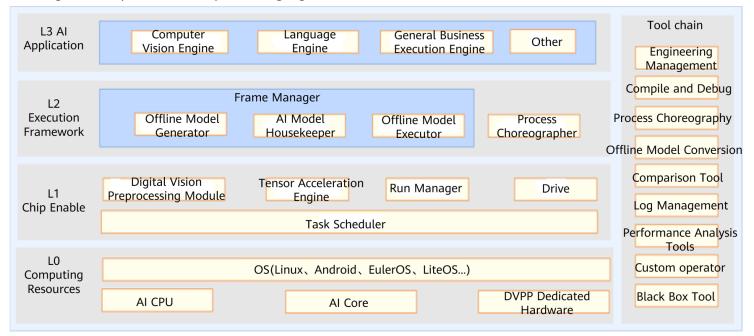

## Logic Architecture of Ascend Al Processor Software Stack (1)

- L3 application enabling layer: It is an application-level encapsulation layer that provides different processing algorithms for specific application fields. L3 provides various fields with computing and processing engines. It can directly use the framework scheduling capability provided by L2 to generate corresponding NNs and implement specific engine functions.

- Generic engine: provides the generic neural network inference capability.

- Computer vision engine: encapsulates video or image processing algorithms.

- Language and text engine: encapsulates basic processing algorithms for voice and text data.

## Logic Architecture of Ascend AI Processor Software Stack (2)

- L2 execution framework layer: encapsulates the framework calling capability and offline model generation capability. After the application algorithm is developed and encapsulated into an engine at L3, L2 calls the appropriate deep learning framework, such as Caffe or TensorFlow, based on the features of the algorithm to obtain the neural network of the corresponding function, and generates an offline model through the framework manager. After L2 converts the original neural network model into an offline model that can be executed on Ascend AI chips, the offline model executor (OME) transfers the offline model to Layer 1 for task allocation.

- L1 chip enabling layer: bridges the offline model to Ascend AI chips. L1 accelerates the offline model for different computing tasks via libraries. Nearest to the bottom-layer computing resources, L1 outputs operator-layer tasks to the hardware.

- L0 computing resource layer: provides computing resources and executes specific computing tasks. It is the hardware computing basis of the Ascend AI chip.

## Contents

- 1. Overview of Al Chips

- 2. Hardware Architecture of Ascend Chips

- 3. Software Architecture of Ascend Chips

- Logic Architecture of Ascend 310

- Neural Network Software Flow of Ascend 310

- Data Flowchart of Ascend 310

- 4. Huawei Atlas Al Computing Platform

- 5. Industry Applications of Atlas

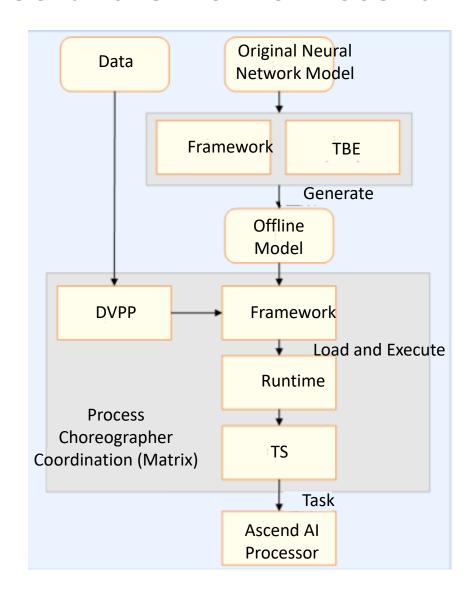

### Neural Network Software Flow of Ascend Al Processors

- The neural network software flow of Ascend AI processors is a bridge between the deep learning framework and Ascend AI chips. It realizes and executes a neural network application and integrates the following functional modules.

- Process orchestrator: implements the neural network on Ascend AI chips, coordinates the whole process of effecting the neural network, and controls the loading and execution of offline models.

- Digital vision pre-processing (DVPP) module: performs data processing and cleaning before input to meet format requirements for computing.

- Tensor boosting engine (TBE): functions as a neural network operator factory that provides powerful computing operators for neural network models.

- Framework manager: builds an original neural network model into a form supported by Ascend AI chips, and integrates the new model into Ascend AI chips to ensure efficient running of the neural network.

- Runtime manager: provides various resource management paths for task delivery and allocation of the neural network.

- Task scheduler: As a task driver for hardware execution, it provides specific target tasks for Ascend AI chips. The operation manager and task scheduler work together to form a dam system for neural network task flow to hardware resources, and monitor and distribute different types of execution tasks in real time.

### Neural Network Software Flow of Ascend Al Processors

## Contents

- 1. Overview of Al Chips

- 2. Hardware Architecture of Ascend Chips

- 3. Software Architecture of Ascend Chips

- Logic Architecture of Ascend 310

- Neural Network Software Flow of Ascend 310

- Data Flowchart of Ascend 310

- 4. Huawei Atlas Al Computing Platform

- 5. Industry Applications of Atlas

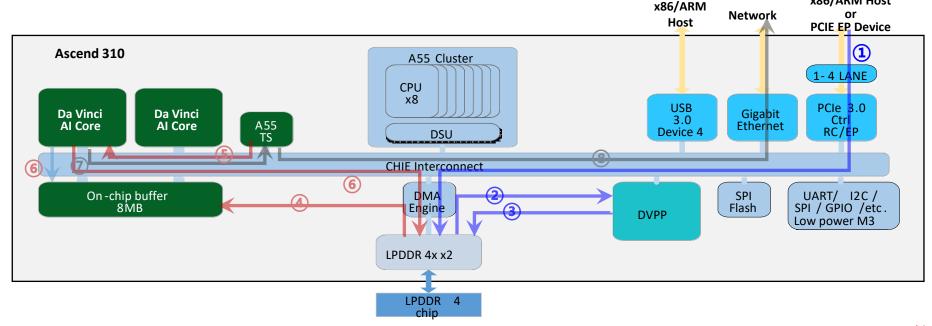

# Data Flowchart of the Ascend AI Processor - Facial Recognition Inference Application (1)

- Camera data collection and processing

- Compressed video streams are transmitted from the camera to the DDR memory through PCIe.

- DVPP reads the compressed video streams into the cache.

- After preprocessing, DVPP writes decompressed frames into the DDR memory.

x86/ARM Host

# Data Flowchart of the Ascend AI Processor - Facial Recognition Inference Application (2)

#### Data inference

- The task scheduler (TS) sends an instruction to the DMA engine to pre-load the AI resources from the DDR to the on-chip buffer.

- The TS configures the AI core to execute tasks.

- □ The AI core reads the feature map and weight, and writes the result to the DDR or on-chip buffer.

- Facial recognition result output

- After processing, the AI core sends the signals to the TS, which checks the result. If another task needs to be allocated, the operation in step (4) is performed.

- When the last AI task is complete, the TS reports the result to the host.

## **Section Summary**

• This section describes the software architecture of Ascend chips, including the LO-L3 software architectures and the neural network software flow of the Ascend AI processor.

## Contents

- 1. Overview of Al Chips

- 2. Hardware Architecture of Ascend Chips

- 3. Software Architecture of Ascend Chips

- 4. Huawei Atlas Al Computing Platform

- 5. Industry Applications of Atlas

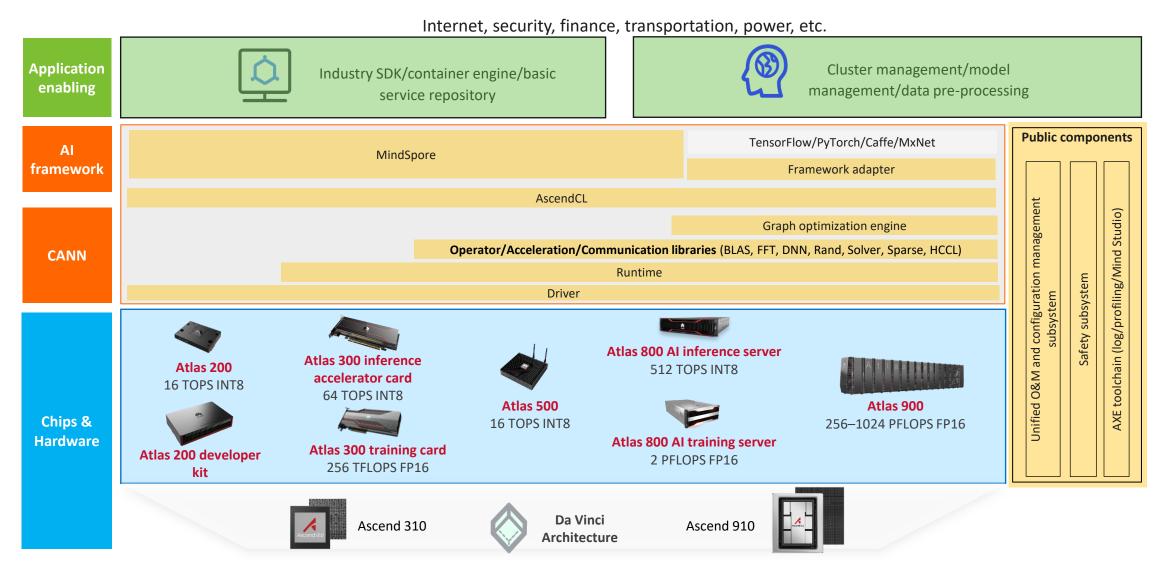

## Overview and Objectives

• This section describes the main products of Huawei Atlas AI computing platform, including inference and training.

## Atlas AI Computing Platform Portfolio

### Atlas Accelerates Al Inference

Ascend 310 Al processor

## Performance improved 7x for terminal devices

Atlas 200 Al accelerator

module

Model: 3000

Highest density in the industry (64-channel) for video inference

Atlas 300 AI accelerator card Model: 3000

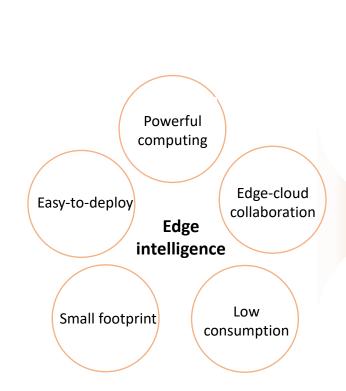

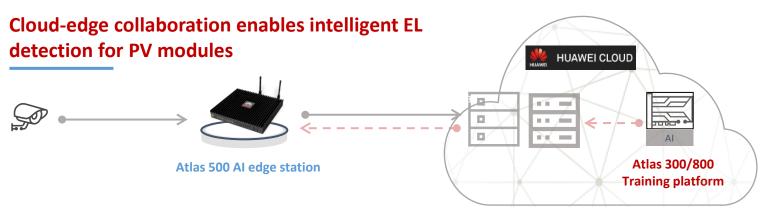

Edge intelligence and cloud-edge collaboration

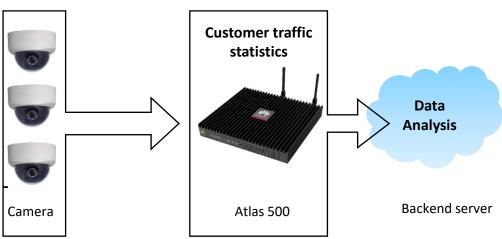

Atlas 500 AI edge station Model: 3000

Powerful computing platform for AI inference

Atlas 800 Al server Model: 3000/3010

Atlas 200 Developer Kit (DK)

Al developer kit

Model: 3000

## Atlas 200DK: Strong Computing Power and Ease-of-Use

Full-Stack AI development on and off the cloud

- 16TOPS INT8 24W

- 1 USB type-C, 2 camera ports, 1 GE port, 1 SD card slot

- 8 GB memory

- Operating temperature: 0°C to 45°C

- Dimensions (H x W x D): 24 mm x 125 mm x 80 mm

#### **Developers**

### Local dev + cloud training collaboration

Same protocol stack for Huawei Cloud and the developer kit; training on the cloud and deployment at local; no modification required

#### Code-level demo

Implementing the algorithm function by modifying 10% code based on the reference architecture; interaction with the Developer Community; seamless migration of commercial products

## Atlas 200DK: Strong Computing Power and Ease-of-Use

- 16 TOPS INT8, 9.5 w

- 16-channel HD video realtime analytics, JPEG decoding

- 4 GB /8 GB memory, four PCle 3.0 interfaces

- Operating temperature: –

25°C to +80°C

Concurrent running of multiple algorithms on Al camera

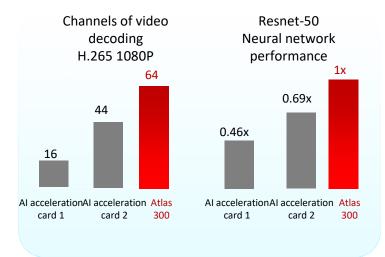

# Atlas 300: Highest-Density, 64-Channel Video Inference Accelerator Card

- 64 TOPS INT8, 67 w

- 32 GB memory

- 64-channel HD video analytics in real time

Model: 3000

## Video Analytics | OCR | Speech Recognition | Precision Marketing | Medical Image Analysis

## Atlas 500 AI Edge Station

- 16 TOPS INT8

- 25 w to 40 w

- Wi-Fi & LTE

- 64-channel HD video analytics in real time

- Fanless design, stable from 40°C to +70°C

#### Atlas 800 Al Server

Model: 3000

Model: 3010

#### An efficient inference platform powered by Kunpeng

#### Key functions:

- 2 Kunpeng 920 processors in a 2U space

- 8 PCIe slots, supporting up to 8 Atlas 300 AI accelerator cards

- Up to 512-channel HD video real-time analytics

- Air-cooled, stable at 5°C to 40°C

#### A flexible inference platform powered by Intel

#### • Key functions:

- 2 Intel® Xeon® SP Skylake or Cascade Lake processors in a 2U space

- 8 PCle slots, supporting up to 7 Atlas 300/NVIDIA T4 AI accelerator cards

- Up to 448-channel HD video real-time analytics

- Air-cooled, stable at 5°C to 35°C

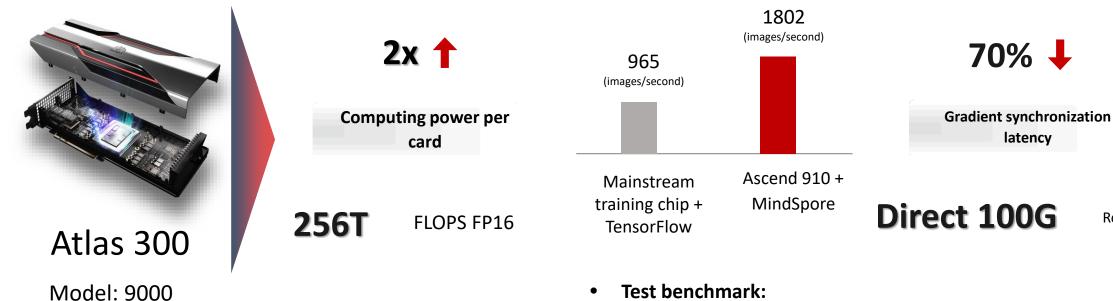

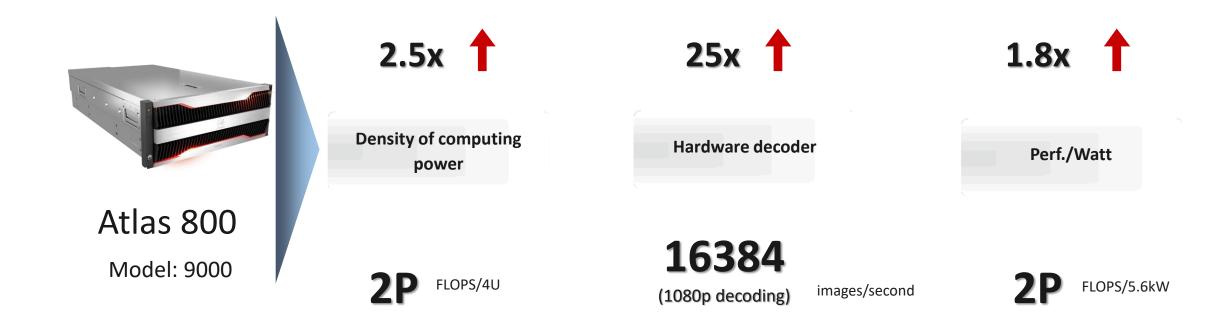

## Atlas Accelerates Al Training

Ascend 910 Al processor

Training card with ultimate computing power

Atlas 300 AI accelerator card Model: 9000

World's most powerful training server

Atlas 800 AI server Model: 9000/9010

World's fastest AI training cluster

Atlas 900 AI cluster

## Atlas 300 Al Accelerator Card: Highest-Performing Accelerator Card for AI Training

#### Test benchmark:

- ResNet 50 V1.5

- ImageNet 2012

- Optimal batch size respectively

**RoCE**

**70% \**

latency

# Atlas 800 Training Server: Industry's Most Powerful Server for Al Training

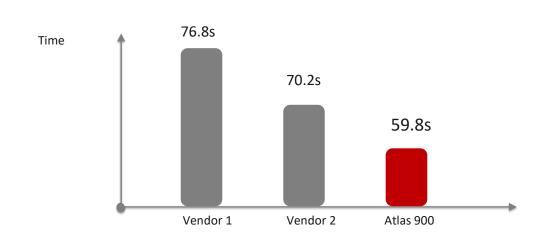

## Atlas 900 Al Cluster: Fastest Cluster for Al Training

Atlas 900

256-1024 PFLOPS FP16

Industry-leading computing power | Best cluster network | Ultimate heat dissipation

#### Shortest time consumption: 59.8s

#### • Test benchmark:

- Benchmark: ResNet-50 V1.5 model, ImageNet-1k

dataset

- Cluster: 1024 Ascend 910 Al processors

- Accuracy: 75.9%

# Atlas Deep Learning System Accelerates AI Model Training and Builds Extensive Applications

Model: 9000

Model: 9000

# Device-Edge-Cloud Collaboration Enables the Ultimate Development and User Experience

**Device-edge-cloud collaboration** for continuous training at data center and remote model update Application system Return unidentified data Video traffic Model file F Deliver inference Remotely update models result Model management 🧻 🖪 Training and inference **Edge inference** and deployment on cloud **Enhanced security Centralized development Centralized O&M** Centralized development architecture based on Transmission channel encryption FusionDirector manages up to 50,000 nodes, **Atlas** Da Vinci and CANN, develop once, deploy Model encryption, double manages central and edge devices, and remotely everywhere pushes models and upgrades devices assurance Edge and data centers use different development No O&M management tools; provides only No encryption/decryption engine; **Industry** architectures. Models cannot transfer freely, APIs, so customers need to develop APIs by models are not encrypted. solution requiring secondary development.

themselves.

## Section Summary

This section introduces products of Huawei Atlas AI computing platform, mainly inference products including Atlas 200 DK, Atlas 200 AI accelerator module, Atlas 300 Al accelerator card, Atlas 500 Al edge station, and Atlas 800 Al server. The computing platforms used for training include Atlas 300 AI accelerator card, Atlas 800 AI server, and Atlas 900 AI cluster.

### Contents

- 1. Overview of Al Chips

- 2. Hardware Architecture of Ascend Chips

- 3. Software Architecture of Ascend Chips

- 4. Huawei Atlas Al Computing Platform

- 5. Industry Applications of Atlas

## Overview and Objectives

• This section introduces industry application scenarios of the Atlas AI computing platform.

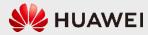

# Electric Power: Industry's First Intelligent Unattended Inspection Solution, with 5x Efficiency

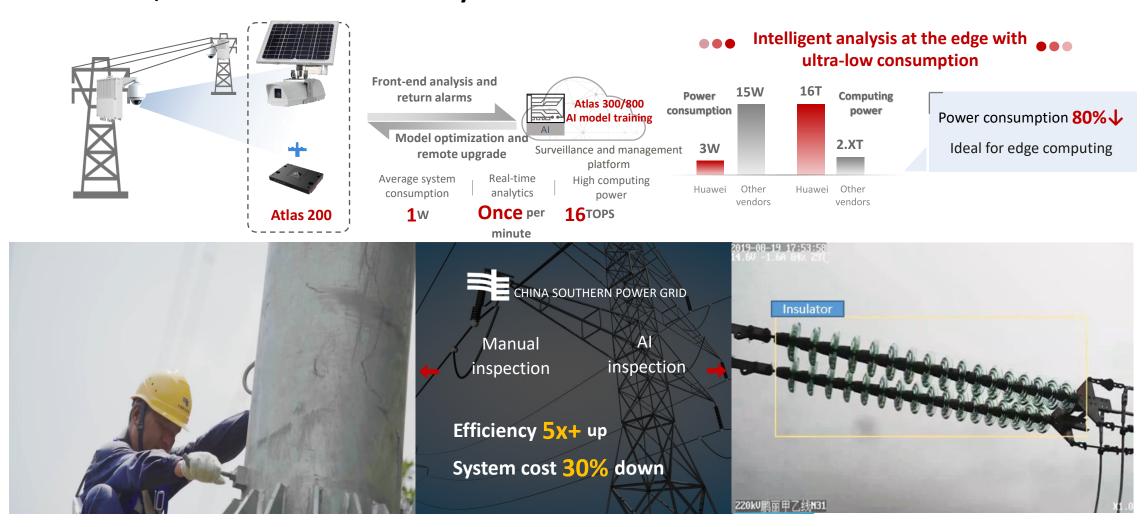

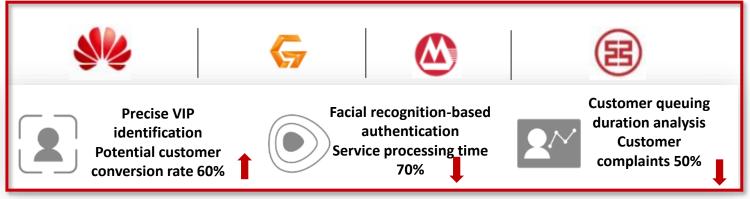

### Finance: Al Enables Smart Branches for Banks

••• **Past:** Customer experience needs improvement

**Now:** cloud-edge collaboration, smart finance

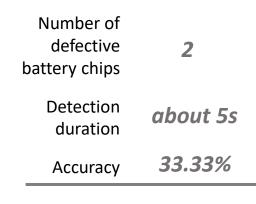

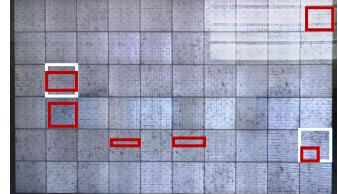

# Manufacturing: AI Enables Intelligent Production Line with Machine Vision

#### **Manual inspection**

| Unstable | Low production | Discontinuous | High labor |  |

|----------|----------------|---------------|------------|--|

| results  | efficiency     | process       | costs      |  |

#### **Smart inspection**

| Zero omission | High production efficiency | Cloud-edge<br>synergy | Reduced labor costs |

|---------------|----------------------------|-----------------------|---------------------|

|               |                            |                       |                     |

Defective

duration

battery chip 6

Detection 1.36s

Accuracy 100%

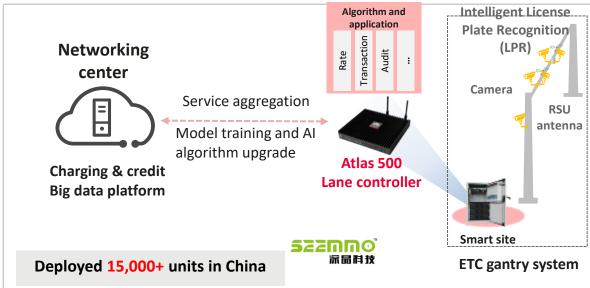

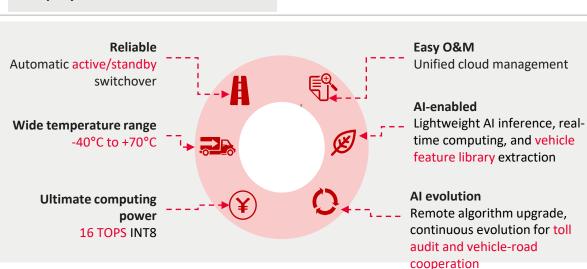

## Transportation: Al Smooths Highways with 5x Efficiency Boost

- Low efficiency

- · Long queuing time

Passing efficiency

5X Saving energy

and reducing

emission

- Proactive security control

- Road cooperation management

- Autonomous vehicle driving

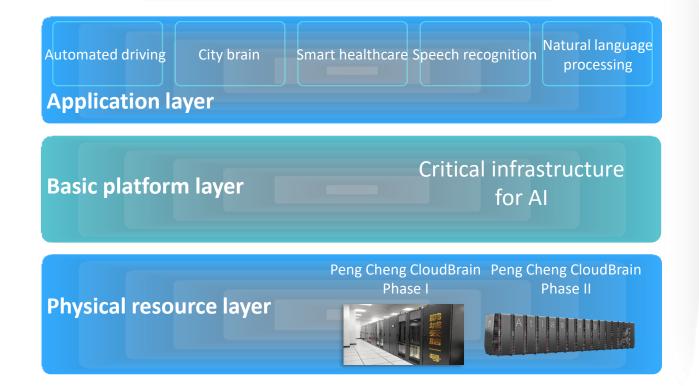

## Supercomputing: Atlas Helps PCL Build CloudBrain Phase II

#### **Peng Cheng Laboratory (PCL)**

Innovative basic platform for national missions

Peng Cheng CloudBrain Phase II mainly built

Atlas 900,

the world's fastest training cluster

#### **Ultimate computing power**

Level-E AI computing power

#### **Top cluster network**

HCCL communication supports 100 TB/s non-blocking parameter plane networking

#### **Ultimate energy efficiency**

Al cluster PUE < 1.1

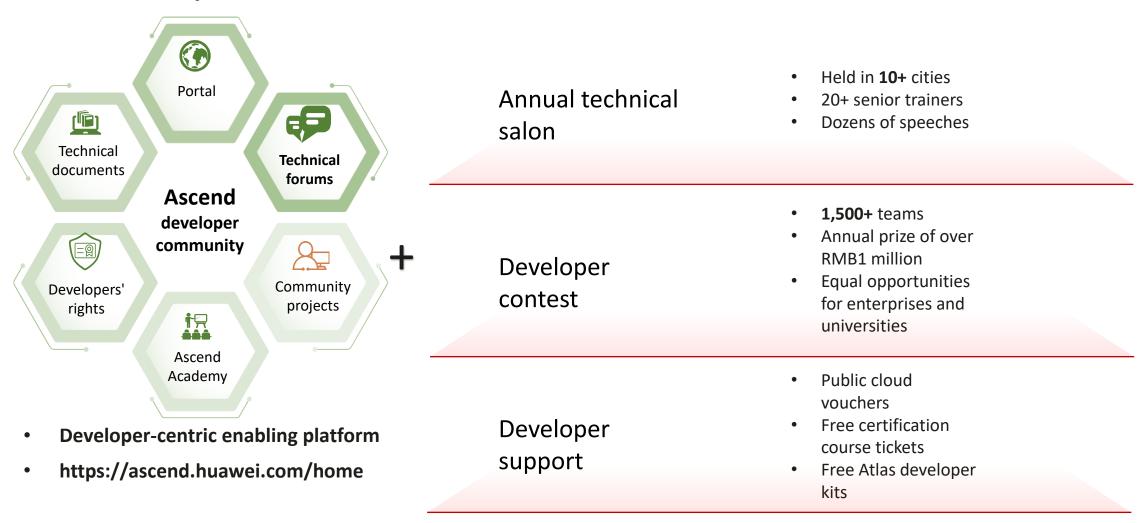

# Attract More Developers Based on the Ascend Developer Community

## Summary

• This chapter describes the products of Huawei Atlas computing platform and helps you to understand the working principles of Huawei Ascend chips. It focuses on the hardware and software architectures of Ascend chips and application scenarios of the Atlas AI computing platform.

## Quiz

- 1. What are the main applications of Ascend 310? ( )

- A. Model inference

- B. Model training

- C. Model building

## Recommendations

- Ascend community:

- https://ascend.huawei.com

## Thank you.

把数字世界带入每个人、每个家庭、每个组织,构建万物互联的智能世界。

Bring digital to every person, home, and organization for a fully connected, intelligent world.

Copyright©2020 Huawei Technologies Co., Ltd. All Rights Reserved.

The information in this document may contain predictive statements including, without limitation, statements regarding the future financial and operating results, future product portfolio, new technology, etc. There are a number of factors that could cause actual results and developments to differ materially from those expressed or implied in the predictive statements. Therefore, such information is provided for reference purpose only and constitutes neither an offer nor an acceptance. Huawei may change the information at any time without notice.